Award bios post коды. Расшифровка кодов POST карты. Коды процедуры перезаписи Flash ROM

Расшифровка кодов POST-карты для "Award BIOS 4.5 "

Award BIOS Version 4.51PG

C0

программирование регистров микросхемы Host Bridge для установки следующих режимов: External Cache запрещен. Запрещено копирование в ячейки External Cache информации, читаемой процессором (все шинные циклы Non Cacheable), а также запрещен просмотр TAGRAM на предмет кэш-попаданий (Force Cache Miss). Internal Cache запрещен. Запрещено формирование сигнала KEN# микросхемой Host Bridge, это запрещает процессору кэшировать читаемые данные. Перед запретом Internal Cache очищается программно либо аппаратно. Shadow RAM запрещено. Это приводит к направлению циклов обращения к адресам расположения System BIOS и Additional BIOS непосредственно на соответствующие ROM , а не Shadow RAM. Данная процедура пишется под конкретный Chipset. Выполняется программирование PIIX ресурсов: Контроллера DMA, контроллера прерываний, таймера, блока RTC. Контроллер DMA переводится в пассивный режим, так как конкретная инициализация каналов (установка базовых адресов, длин блоков, режимов передачи) задача не POST, а программ поддержки периферийных устройств, выполняемых уже по ходу рабочего сеанса. Контроллер прерываний настраивается следующим образом.

Master Controller (IRQ0-IRQ7)

:

режим векторных прерываний, прием запроса по фронту IRQ в соответствии IRQ0=INT8...IRQ7=INT0Fh.

Slave Controller (IRQ8-IRQ15)

:

режим векторных прерываний, прием запроса по фронту IRQ в соответствии IRQ8=INT70h...IRQ15=INT77h.

На этом этапе происходит только подготовка контроллера прерываний к работе, сами прерывания запрещены, и разрешаются существенно позже, предположительно, после теста памяти 31 Таймер настраивается следующим образом.

Counter 0

: генерация запросов IRQ0 для подсчета DOS Time, устанавливается режим деления частоты на 65536, в результате частота IRQ0 равна 18.2 Hz.

Counter 1

: генерация запросов DRAM Refresh, устанавливается режим деления частоты на 20, в результате интервал между регенерацией двух строк DRAM около 15 мкС, т.е. 128 циклов выполняется за 2 мС.

Counter 2

: Используется для звука. На данном этапе просто переводится в пассивное состояние, установка параметров этого счетчика происходит при выдаче сигнала на системный динамик.

Подсистема Real Time Clock нуждается в инициализации только в случае, если произошел сбой батарейного питания. Иначе полная инициализация CMOS не выполняется, потому что это приводило бы к сбросу часов при каждом включении. Если сбоя VCC(BAT) не было, инициализируются только регистры, отвечающие за взаимодействие RTC и процессора, но не сами часы

С1

Путем последовательных записей и контрольных считываний определяется тип памяти, суммарный объем и размещение по строкам. Результатом этого шага является настройка следующих параметров DRAM контроллера:

тип памяти (SDRAM, EDO, FPM);

картирующая информация (в зависимости от расположения по Socket);

значение параметра Memory.

Если адрес, сформированный процессором, превышает Memory , данный цикл направляется на PCI. Более точная настройка временнЫх параметров DRAM выполняется позже, в соответствии с содержимым Setup RAM либо SPD

C3

Проверка первых 256К DRAM для организации Temporary Area. Распаковка System BIOS в DRAM, копирование Option ROMs в DRAM. Этот этап выполняется для подготовки к операции Shadow. Необходимость в Temporary Area связана с тем, что Shadow блоки ОЗУ, закрепленные за соответствующими ПЗУ, включаются на те же диапазоны адресов, что и сами ПЗУ, из-за этого нельзя выполнить пересылку (распаковку) за один прием, потому что читать надо ROM, а записывать в Shadow RAM. Поэтому вначале на соответствующий диапазон картируется ROM и выполняется пересылка (распаковка) в транзитный буфер Temporary Area, затем перепрограммируется Host Bridge так, чтобы на область адресов BIOS картировать Shadow RAM и из транзитного буфера код переносится в Shadow RAM. На этапе C3 тестируются первые 256 Кбайт DRAM, которые в дальнейшем будут использованы как транзитный буфер.

Выполняется проверка контрольных сумм и наличие метки BBSS. Если метка не обнаружена или контрольные суммы не совпадают, принимается решение о частичном повреждении микропрограмм BIOS. Управление передается на подпрограмму восстановления FlashROM, расположенную в BootBlock. (BootBlock POST Codes)

C5

Выполняемый код POST переносится в Shadow RAM и далее выполняется из Shadow RAM для ускорения прохождения POST.

Shadow RAM быстрее ROM по двум причинам: разрядность ROM 8 бит, разрядность RAM равна разрядности локальной шины данных процессора. Время выборки используемых DRAM существенно меньше аналогичного параметра используемых ROM / Flash ROM

C6

Определение присутствия, объема и типа External Cache. Наличие и параметры External Cache определяются путем записей и контрольных считываний по специальному алгоритму

C8

Проверка целостности компонентов BIOS, расположенных в ROM. В случае несовпадения контрольной суммы компонентов делается вывод о повреждении области 128 Кб, содержащей внешний по отношению к системному BIOS файл awardext.rom. В виду того, что системный BIOS хранится в следующем 128 Кб блоке, некоторые 2 Мбит BIOS могут корректно обрабатывать эту ошибку и передавать управление на программу восстановления.

CF

Определение типа процессора. Результат помещается в CMOS. В виду того, что не все RTC инициализируются к этому моменту, сначала выполняется тест чтения/записи.

Если по каким либо причинам определение типа CPU закончилось неудачей, такая ошибка становится фатальной и POST дальше не выполняется и система останавливается.

01

В ранних версиях BIOS выполнялась проверка флагов признаков результата арифметической операции по такому алгоритму: флаги переноса (CF), нуля (ZF), знака (SF), переполнения (OF) принудительно устанавливаются в 1 командой SAHF, после этого проверяется что команды условного перехода JC, JZ, JS, JO выполняются. Затем подобным образом проверяется правильность отработки условных переходов при нулевых значениях этих флагов. Позднее от этого отказались по причине того, что неправильная работа флагов является очень грубой ошибкой процессора, при наличии которой POST все равно не дойдет до этого теста. Кроме того, начиная с 80386, процессоры имеют автономный тест, и при наличии такой грубой ошибки маловероятно, что процессор начнет выполнение POST вообще.

02

Зарезервировано для ProcessorTest 2. Проверка регистров процессора путем записи и контрольного считывания. От этого теста отказались приблизительно на этапе 80386 по той же причине, что и для теста 01

.

03

Предполагается, что верен вариант Soyo, согласно которому выполняется только настройка EISA ресурсов, а PIIX ресурсы (DMA, INT, Timer, RTC) настраиваются на шаге C0

, как это было описано выше, однако в зависимости от конкретной версии BIOS могут быть вариации.

NMI (Non Maskable interrupt) немаскируемое прерывание, имеет фиксированный номер вектора (2), используется для сообщения процессору об аварийных ситуациях (ошибка четности DRAM, активность сигнала IOCHCK# на ISA и т.п.).

PIE

, AIE

, UIE

(в исходном документе Award опечатка, по ошибке указано UEI) - это три разрешающих бита для формирования запроса прерывания схемой RealTimeClock (IRQ8 = INT 70h), по трем условиям, которые можно взаимонезависимо разрешать и запрещать.

PIE

(Periodic Interrupt Enable

) - разрешение периодических прерываний с программно устанавливаемой частотой.

AIE

(Alarm Interrupt Enable

) - разрешение прерываний от будильника, формируемых при совпадении значений часов, минут, секунд в регистрах подсчета времени и регистрах будильника.

UIE

(Update Interrupt Enable

) - разрешение прерываний при завершении цикла обновления состояния счетчиков часов:минут:секунд (1 раз в секунду).

SQWV

- режим генерации программируемой частоты на специальном выходе микросхемы RTC. PIE, AIE, UIE, SQWV запрещаются при выполнении POST, для этого записывается соответственно управляющий байт в регистр 0Bh микросхемы RTC.

04

Проверка формирования запросов на регенерацию DRAM.

В классической реализации PC AT запросы на регенерацию DRAM генерирует канал 1 системного таймера 8254. К его выходу также подключен триггер, работающий в счетном режиме и меняющий свое состояние на противоположное при каждом запросе. Состояние этого триггера можно программно считывать через бит 4 порта 61h. Проверка Refresh Toggle заключается в проверке того факта, что этот триггер переключается с заданной частотой. Однако появились chipset, использующие другие алгоритмы регенерации DRAM, с целью свести к минимуму простои CPU из-за регенерации. В этом случае, несмотря на то, что Refresh Trigger сохраняется для совместимости, по нему уже нельзя проверить формирование запросов на регенерацию.

Начиная с этого момента становится возможным использование стека

05

Если установлены адаптеры EGA или VGA, поддерживаемые собственным BIOS, операция Blank Video на этом этапе невозможна, так как Video BIOS еще не инициализирован. Если установлены CGA или MDA, обслуживаемые процедурами видео сервиса System BIOS, теоретически есть возможность очистить экран на этом шаге.

Проверка и инициализация контроллера клавиатуры. Контроллеру клавиатуры передается команда самотестирования и контролируется статус после ее завершения. Затем передается команда разрешения интерфейса клавиатуры.

Примечание 1

:

На данный момент прием кодов нажатых клавиш еще невозможен, так как запрещены прерывания, не подготовлены области данных BIOS, не инициализирована сама клавиатура.

06

Тест Shadow области памяти, начинающейся с адреса F000h, где размещен BIOS. Предположительно выполняются некоторые действия направленные на дополнительную проверку памяти или содержимого памяти, так как если на шаге C5

в Shadow RAM размещен BIOS, тестировать его уже поздно. Возможно, данный шаг обусловлен спецификацией конкретного ChipSet либо присутствует в BIOS, не поддерживающих Early Shadow.

07

Проверка функционирования CMOS и батарейного питания.

Батарейное питание проверяется путем чтения регистра 0Dh микросхемы RTC. Бит 7 этого регистра индицирует ошибку батарейного питания, причем он сообщает об ошибке, даже если в данный момент питание CMOS в норме, но с момента последнего считывания регистра 0Dh имело место пропадание питания CMOS. Если зафиксирована ошибка питания, BIOS запоминает этот факт, но POST не останавливается. Затем выполняется Verify Basic R/W functionality - проверка ячеек CMOS как проверка памяти. Записываются значения, выполняется контрольное считывание и проверяется равенство читаемого кода записанному. В отличие от ошибки батарейного питания, ошибка, выявленная этой проверкой считается фатальной и приводит к остановке на коде 07

.

BE

Настройка конфигурационных регистров CHIPSET. Программирование конфигурационных регистров микросхем Host Bridge и PIIX. Значения загружаются из таблицы BIOS defaults, доступной пользователю с помощью утилиты MODBIN .

08

В сложившемся разногласии видимо верное значение Absent, в виду того, что 64К, о которых здесь идет речь, уже протестированы, так как входят в 256К, задействованных на шагах C3

, C5

. OEM Specific действия по первичной настройке DRAM Controller соответственно уже проделаны.

09

Процессоры IBM/Cyrix имеют внутренние регистры для более гибкого управления кэшированием. На этом шаге выполняется машинная команда CPUID для распознавания типа процессора (видимо, основная процедура распознавания CPU происходит существенно позже, на данном этапе следует выяснить IBM/Cyrix это или нет), если распознан IBM/Cyrix, инициализируются его регистры расширенного управления кэшированием.

Выполняется инициализация L2 Cache Controller (запись управляющих слов в соответствующие регистры конфигурационного блока Host Bridge, очистка TAGRAM).

0A1

Генерация таблицы векторов прерываний. Таблица имеет объем 1024 байта и содержит 256 указателей на процедуры обработки прерываний, на каждую процедуру - два 16-битовых слова: смещение и сегмент, на данном этапе устанавливаются 32 вектора (INT 00h - INT 1Fh), на процедуры обработки соответствующих прерываний (Interrupt Handlers), входящие в состав BIOS. Векторы 33-120 устанавливаются на процедуру заглушку. Настройка ресурсов Power Management. На этом шаге также происходит первичная настройка подсистемы управления питанием, входящей в состав PIIX, схемы генерации SMI (System Management interrupt) и установка вектора SMI .

0B

Если нажата клавиша INS, выполняется установка CMOS по умолчанию.

Существенно важный момент для BIOS, поддерживающих SoftMenu. (См. FAQ №9

) .

Проверяется контрольная сумма блока ячеек CMOS, отвечающего за хранение конфигурационной информации, если фиксируется ошибка, устанавливается программный флаг CMOS недостоверен. Этот флаг также устанавливается, если ранее, на шаге 07

было выявлено пропадание батарейного питания CMOS.

Если BIOS поддерживает PnP, выполняется сканирование ISA PnP устройств и инициализация их параметров (Адрес, Номера IRQ и DRQ). Для PCI устройств устанавливаются основные параметры в блоке конфигурационных регистров (PCI Bus Cycle parameters, I/O and MEMORY Address). Блок конфигурационных регистров PCI устройства содержит поля, имеющие одинаковое назначение у всех PCI устройств (стандартные) и поля, специфичные для конкретного устройства. Установка параметров PCI устройств, о которой здесь идет речь сводится к установке значений стандартных полей.

В процессорах класса P6 существует доступ к памяти микропрограмм, в которой хранится микрокод для выполнения каждой машинной команды. Внесение изменений в микрокод, дает возможность изменять алгоритмы выполнения имеющихся машинных команд и добавлять новые.

0C

Инициализация блока переменных BIOS. На этом этапе присваиваются стартовые значения переменным BIOS, находящимся в 256-байтовом блоке 0040:0000h - 0040:00FFh.

Разногласия с Initialize Keyboard, видимо решаются в пользу варианта Soyo, так как второе после включения питания мигание светодиодов клавиатуры происходит уже после инициализации видеоадаптера

0D

Классический подход к обнаружению видеоадаптера следующий: проверяется наличие EGABIOS или VGABIOS путем проверки наличия сигнатуры 55 AA по адресу начала Video BIOS (Seg:Offs

= C000:0000h

). Если сигнатура обнаружена, проверяется контрольная сумма Video BIOS, если она правильная, происходит передача управления командой CALL FAR по адресу Seg:Offs = C000:0003h на инициализационную процедуру Video BIOS. Эта процедура настраивает видеоадаптер, переустанавливает вектор прерывания INT 10h (Video Service) на сервисную процедуру Video BIOS, выдает заставку видеоадаптера и возвращает управление вызвавшей процедуре System BIOS командой RET FAR. Если Video BIOS не обнаружен, делается попытка обнаружить CGA или MDA, путем сканирования пространства портов и поиска регистров управления CGA/MDA. Если CGA или MDA обнаружены, BIOS инициализирует видеоадаптер. В отличие от EGA/VGA, у CGA/MDA адаптеров Video BIOS нет и обработка INT 10h для CGA/MDA входит в обязанности System BIOS. Если не обнаружен никакой видеоадаптер - генерируется звуковой сигнал.

На этом же этапе происходит распознавание типа процессора (процессоров) настройка I/O APIC, Local APIC, программирование Host Bridge для установки параметров Host Bus (Front Side Bus). Для распознавания типа процессора обычно используется команда CPUID.

Для измерения тактовой частоты используется измерение частоты инкрементирования регистра TSC (Time Stamp Counter), который инкрементируется по каждому такту Internal CPU CLK. В качестве генератора образцовой частоты может использоваться либо системный таймер, либо RTC. Некоторые BIOS не используют Time Stamp Counter, а измеряют время выполнения цикла из последовательности команд, для которых известно количество тактов на команду. Так делалось, когда процессоры не имели TSC

0E

Если установлен видеоадаптер CGA или MDA, выполняется тест Video RAM. Для EGA/VGA такой тест был проделан Video BIOS на шаге 0D

, при выполнении инициализационной процедуры C000:0003h

.

Относительно настройки APIC: скорее всего она разбита на два этапа, выполняемых на шагах 0D

и 0E

.

Предположительно на этом шаге, а не 0F

, настраивается клавиатура и разрешаются аппаратные прерывания от таймера 8254 (IRQ0) и клавиатуры (IRQ1).

Инициализация RPB (Remote Pre Boot) подсистемы удаленной загрузки,

0F

Проверка первого контроллера DMA 8237, ошибочно указанного в документации SOYO канал 0 - перепутаны понятия "канал DMA" и "контроллер DMA". Проверка выполняется путем записи и контрольного считывания регистров базового адреса и длины пересылки. Собственно тестовых пересылок данных с помощью DMA каналов на этом шаге и вообще в POST не выполняется. Таким образом проверяется только чтение/запись регистров контроллера DMA процессором с помощью команд IN / OUT.

BIOS Checksum должен был проверяться при распаковке, видимо расположение BIOS Checksum Test на этом этапе было до того, как BIOS разделили на Boot Block и основной (упакованный) блок.

Известно, что на этом этапе выполняется определения клавиатуры и ее внутренний тест. Запрещены Reset контроллера клавиатуры и обслуживаемый им интерфейс манипулятора "мышь" PS/2. Эти действия выполняются позже на шаге 3D.

10

Проверка второго контроллера DMA 8237.

11

Проверка страничных регистров контроллеров DMA. Страничные регистры необходимы для расширения 16-битового адреса формируемого контроллером 8237 до 24-битового (ISA) или 32-битового (EISA).

Обособление страничных регистров от контроллера DMA обусловлено тем, что в старых системах использовался контроллер DMA Intel 8237 в виде отдельной микросхемы, он способен формировать только 16-битовые адреса, поэтому устанавливался дополнительный блок расширения адреса (DMA Page Registers).

Тест страничных регистров выполняется путем записей и контрольных считываний, без собственно DMA операций (пересылок)

14

Тест канала (счетчика) 2 системного таймера. Канал 2 системного таймера используется для генерации звука. По нашим сведениям какого-либо классического подхода к этому тесту не сформировано, некоторые BIOS ограничиваются записью и контрольным считыванием регистров таймера, доступных для записи и чтения (R/W test).

Некоторые BIOS программируют таймер на формирование заданного интервала и контролируют длительность сформированного интервала по часам RTC. Однако в случае расхождения не понятно кто ошибся - Timer или RTC. Предположительно, Award 4.51 ограничился R/W тестом,

15

Проверка регистра маскирования запросов первого контроллера прерываний. Следует сказать, что использование термина "Channel" для контроллера прерываний нетрадиционно и приведет к путанице. Приняты следующие обозначения: Первый контроллер прерываний (Master), 8259#1. Регистры доступны по адресам 20h, 21h. Обрабатывает IRQ0-IRQ7, которым присвоены вектора INT 08h - INT 0Fh. Второй контроллер прерываний (Slave), 8259#2. Регистры доступны по адресам A0h, A1h. Обрабатывает IRQ8-IRQ15, которым присвоены вектора INT 70h - INT 77h. Выход Slave8259 подключен ко входу IRQ2 Master 8259.

На этом шаге проверяется регистр маскирования первого контроллера прерываний путем записи тестовых кодов в порт 21h и контрольного считывания. Однако проверки собственно операции маскирования, как индивидуального разрешения/запрещения линий IRQ POST не выполняет.

16

Проверка регистра маскирования запросов второго контроллера прерываний. Операция аналогична шагу 15

, адрес регистра маскирования для второго контроллера прерываний - A1h.

17

Зарезервировано. Видимо у более ранних версий BIOS на этом шаге выполнялась следующая операция: устройства источники IRQ (Timer, Keyboard...) программировались таким образом, чтобы запрос IRQ зафиксировался в пассивном состоянии, затем выполнялось чтение регистров запросов контроллеров прерываний 8259#1 и 8259#2 и проверялся тот факт, что соответствующие запросы пассивны.

Практика ремонта плат, показывает, что фиксация IRQ в состоянии 0 или 1 дает о себе знать только в момент, когда нужно взаимодействовать с устройством, IRQ которого неисправно (так происходит в большинстве случаев). На этапе теста контроллера прерываний такой дефект НЕ выявляется, поэтому предполагается, что BIOS не делает указанного действия.

18

По описанию этот шаг подобен шагу 17

, однако, если на шаге 17

проверялось отсутствие запросов, то здесь наоборот, устройства источники IRQ программируются на активизацию запросов и проверяется запуск процедур обработки прерывания для активизированных запросов.

На основании тех же экспериментальных данных, о которых шла речь в описании шага 17

, можно считать, что шаг 18

действительно отсутствует в том смысле, который имеет в виду Award. Имеется подтверждение о его существовании и выполнении совершенно иных тестовых процедур, связанных с определением типа процессора.

19

Проверка пассивности запроса немаскируемого прерывания (NMI). Запрос NMI используется для сообщения процессору об аварийных ситуациях (ошибка четности памяти, активность сигнала #IOCHCK на шине ISA). Он приводит к генерации прерывания с фиксированным номером вектора - 2 и обрабатывается без участия 8259. Указанные аварийные события приводят к установке триггера NMI, сброс этого триггера выполняется программно, его состояние также можно опросить (используется порт 61h). Обычно этот тест подразумевает выполнение программного сброса триггера NMI и проверку, что он не установился повторно

1A

Предположительно, что этот шаг Reserved, а вывод на экран значения тактовой частоты CPU происходит на шаге 0D.

1E

, 1F

Установка параметров шины EISA в соответствии с содержимым NV memory (EISA BIOS). Проверяется контрольная сумма блока параметров EISA (NVM Checksum), если она верная, контроллер EISA инициализируется в соответствии с указанными параметрами.

20

...2F

Инициализация EISA устройств. В отличие от ISA, шина EISA имеет средства для индивидуальной адресации слотов (раздельные сигналы SELECT). Таким образом, имеется возможность программно распознать, в каком слоте какое устройство установлено. Возможно также выполнить раздельный доступ к конфигурационным регистрам подобно PCI, что и делается на этом шаге

.

30

1

.Get Base Memory and Extended Memory Size

2.P6 Multi-P BIOS Only - Init I/O and Local APIC

3.Program K5/K6 CPU"s Write Allocation

Определение объема Base Memory и Extended Memory. Это завершающая стадия определения объема памяти, к этому моменту все операции по картированию выполнены, и на этой стадии уже начинается тестирование памяти, BIOS выполняет запись/контрольное считывание, определяет, начиная с какого адреса прекращается совпадение читаемых значений записанным и этот адрес принимается как граница памяти.

Настройка APIC применительно к P6 освещена достаточно мало.

K5/K6 Write Allocation

- это нововведение AMD, которое сводится к следующему. У процессоров Intel поводом для кэширования ячейки является только ее чтение, после того, как ячейка с определенным адресом кэширована, это приносит пользу также и при записи (Write Back), однако само кэширование выполняется только при чтении, поэтому если в выполняемом коде попадается серия из последовательных записей по одинаковым (или близким) адресам, кэш не приносит пользы, если до этого эти адреса не считывались программой. AMD Write Allocation - режим, при котором поводом для кэширования является не только чтение данных, но и запись. Это чревато коллизиями, как любое отступление от стандарта Intel, поэтому AMD предусмотрела возможность программного управления этим режимом, вплоть до отключения его. Настройка регистров процессоров AMD K5/K6, управляющих этим режимом, и есть часть шага 30.

31

1. Test base memory from 256K to 640K and extended memory above 1MB .

2. Test Extended Memory from 1M to the of memoryusing various patterns.

NOTE: This will be skipped in EISA mode and can be "skipped" with ESC key in ISA mode.

3. USB Init .

Основной отображаемый на экране тест оперативной памяти. Для объема памяти, определенного на шаге 30

выполняется тест, путем записи нескольких видов Pattern и их контрольного считывания. Предположительной причиной разногласий по EISA является тот факт, что по старым стандартам, иметь более 16 Мбайт памяти могла только EISA система. Сейчас это не так, и вся физически присутствующая память тестируется на этом этапе, во всяком случае для не EISA системы.

Инициализация USB. По USB есть сомнения: это действие не имеющее отношение к тесту памяти и для него должны были зарезервировать отдельный код.

32

IfEISA Mode flag is set then test EISA memory found in slots initialization.

NOTE: This will be skipped in ISA mode and can be "skipped" with ESC key in EISA mode.

Display the Award Plug and Play BIOS Extension message (PnP BIOS ONLY).

Program all onboard super I/O chips(if any) including COM ports, LPT ports, FDD port... according to setup value Program onboard audio devices

Если исходить из предположения, что вся память проверяется на шаге 31

, то для шага 32

верным кажется вариант Soyo, где нет упоминаний про память.

Выводится заставка Plug and Play BIOS Extension

.

Настройка ресурсов Super I/O. Микросхема SIO вводится в режим конфигурирования. В соответствии с установками Setup, если CMOS достоверен, программируются параметры: базовые адреса программно-доступных ресурсов COM, LPT, FDC, GamePort номера используемых линий IRQ и DRQ. После этого отключается режим конфигурирования SIO.

Аналогично программируется Onboard Audio Device. Если Audio Device подключено к PCI, его настройка происходит не на этом шаге, а на шаге 0B .

39

Programming clock synthesizer by I2C bus

.

Предположительно, на этом шаге выполняется программирование тактового генератора по шине I2C

3C

Set flag to allow users to enter CMOS Setup Utility.

Установка программного флага разрешения входа в Setup.

3D

1. Initialize Keyboard.

2. Install PS2 mouse .

3. Build the INT 15h function E820H table .

4. Build the PnP Device Node for total memory size .

Инициализация PS/2 mouse. Один из альтернативных моментов для инициализации клавиатуры.

Относительно функции E820h и PnP Device Node информации мало.

3E

Try to turn on Level 2 cache.

NOTE: Some chipset may need to turn on the L2 cache in this stage. But usually, the cache is turn on later in POST 61h.

Один из альтернативных моментов для инициализации контроллера External Cache и разрешения Cache

BF

1. Program the rest of the Chipset"s value according to Setup (Later Setup Value Program).

2. If auto-configuration is enabled, programmed the chipset with pre-defined values in the MODBINable Auto-Table

.

Настройка конфигурационных регистров CHIPSET в соответствии с установками CHIPSET Setup.

Доступно для утилиты MODBIN.

40

Display virus protect disable or enable - Absent

.

Отображение состояния опции Virus Protect, исключено в новых версиях BIOS

41

Initialize floppy disk drive controller and any drives.

Инициализация подсистемы гибких дисков.

Для BIOS поддерживающих процессоры P6 сначала выполняется отключение local APIC, потому что в противном случае запрос IRQ не может быть правильно сгенерирован. Затем, для всех типов BIOS, выполняется программный сброс контроллера дисковода (через порт 3F2h). Снимается маскирование запроса прерывания от дисковода (IRQ6), для этого обнуляется бит 6 в порте 21h, проверяется прохождение запроса прерывания от контроллера дисковода. Устанавливаются параметры работы контроллера дисковода (командой SPECIFY). Если в Setup разрешен Floppy Drive Seek Test, выполняется тест позиционирования для установленных дисководов

42

1. Cut IRQ 12 connection if PS2 mouse is not installed.

2. Install IDE Hard Drives. Auto-detect HDDs. Build the AT compatible HDD table for Type 47. Set PIO timing

.

3. Detect CD ROM on IDE Bus

.

4. Detect LS120 drive

.

Отключение IRQ12 если PS/2 mouse отсутствует.

Выполняется программный сброс контроллера жестких дисков. Если для устройства в Setup указан режим AUTO, выполняется команда IDENTIFY DRIVE, иначе параметры устройства берутся из CMOS. Выполняется программирование конфигурационных регистров PIIX для установки PIO Mode.

Выполняется сканирование на предмет наличия других IDE устройств (CDROM, LS120 ...). Если на Primary IDE присутствуют устройства, размаскируется IRQ14, обнуляется бит 6 в порте A1h. Если на Secondary IDE присутствуют устройства, размаскируется IRQ15, обнуляется бит 7 в порте A1h. Проверяется прохождение соответствующих IRQ (только для HDD)

43

1. Detect and Initialize Serial/Parallel Ports (also game port).

2. If it is a PNP BIOS, initialize serial and parallel ports

.

Предположительно само конфигурирование Si/o Chip происходит на шаге 32

, а на шаге 43

ресурсы SIO вносятся в формируемый BIOS список PnP устройств.

45

Detect and Initialize math coprocessor.

Инициализация сопроцессора FPU.

Проверка наличия (Detect) в обычном понимании не выполняется, так как наличие/отсутствие FPU однозначно следует из информации, прочитанной по команде CPUID при определении CPU Type. Но в силу того, что убедиться в функциональной пригодности этого устройства невозможно на ранних этапах POST, выполняется ряд тестов с участием памяти, подтверждающих корректность определения FPU.

Под инициализацией обычно понимается программный сброс FPU и запись управляющего слова в регистр FPU CW .

4E

1. Reboot if Manufacturing pin POST Loop is set. Otherwise display any messages (i.e., any non-fatal errors that were detected during POST) and enter Setup.

2. If there is any error detected (such as video, keyboard etc.), show all the error messages on the screen and wait for user to press key .

3. Enable "Far Hit" for IBM/Cyrix 6x86 CPU.

Инициализация клавиатуры USB.

Некоторые материнские платы (в основном в конструктиве Socket 7) имеют перемычку для заводского тестирования. Если указанная перемычка установлена, выполняется перезагрузка. В противном случае на экран выводятся сообщения о нефатальных ошибках, таких как несоответствие HDD объявленному в CMOS типу, отказе клавиатуры и тому подобное.

На данном этапе становится возможен вход в CMOS Setup, если отработано нажатие клавиши DEL.

В случае, если перемычка заводского тестирования не установлена либо не предусмотрена вообще и обнаружены ошибки, не препятствующие дальнейшему выполнению POST и старту операционной системы, выводится сообщение и ожидание продолжить POST по нажатию любой клавиши. Для клавиатуры в стандарте DIN или PS/2 инициализация уже выполнена на шаге 3D

, поэтому выполняется только проверка состояния KeyLock. Прочие параметры клавиатуры устанавливаются на шаге 62

.

В связи с тем, что на шаге 45

завершены все инициализационные процедуры для CPU, становится возможным выбрать протокол работы с cache L2, если установлен процессор IBM/Cyrix. Разрешается Write Allocation .

4F

1. If password is needed, ask for password.

2. Clear the Energy Star Logo (Green BIOS ONLY) .

Запрос на ввод пароля, если это предусмотрено установками CMOS Setup.

Логотип Energy Star Pollution или его заменяющий исчезает.

50

Write all CMOS values back to RAM and clear screen.

Write all the CMOS values currently in the BIOS stack area back into the CMOS .

Восстановление ранее сохраненного в ОЗУ состояния CMOS. При выполнении некоторых фрагментов POST содержимое CMOS может модифицироваться, поэтому исходное содержимое CMOS копируется в ОЗУ, обычно стек BIOS, а после прохождения искажающих CMOS фрагментов, записывается обратно в CMOS .

51

Enable parity checker, Enable NMI, Enable cache, reset flags before boot.

Относительно разрешения контроля четности, немаскируемых прерываний, cache L1/L2 и переустановки флагов информации нет. Предположительно, выполнение указанных операций возможно только для чип сетов типа Intel HX, осуществляющих поддержку контроля четности.

Разрешено автоопределение HDD по схеме с 32-битным доступом.

Инициализация и установка параметров устройств ISA/PnP до инициализации устройств PCI

52

1. Initialize any option ROMs present from C8000h to EFFFFh

.

NOTE: When FSCAN option is enabled, will initialize from C8000h to F7FFFh

.

2. Later PCI initializations (PCI BIOS ONLY) - assign IRQ to PCI devices - initialize all PCI ROMs.

3. Program shadows RAM according to Setup settings.

4. Program parity according to Setup setting.

5. Power Management Initialization. Enable/Disable global PM - APM interface initializtion.

Инициализация ПЗУ дополнительных BIOS (ROMSCAN процедура). В диапазоне адресов C8000H-EFFFFH

выполняется поиск сигнатур дополнительных BIOS (55 AA), если сигнатура обнаружена, считывается байт длины блока (идущий после сигнатуры) для блока проверяется контрольная сумма, и в случае верной контрольной суммы управление передается командой FAR CALL по смещению 0003 относительно начала блока. Предполагается, что дополнительный BIOS выполнит инициализацию устройства, которое он обслуживает, перехватит необходимые вектора прерываний и вернет управление в System BIOS командой RET FAR. Типичный пример - SCSI BIOS, который обычно перехватывает INT 13h и берет на себя обслуживание SCSI HDD. Video BIOS использует ту же идеологию, но находится на особом положении - его инициализация происходит раньше, для обеспечения возможности отображения выполнения POST на экране.

Assign IRQ to PCI devices - имеется в виду установка значений четырех конфигурационных регистров PIIX (по числу линий PCI INT), в которые записывается, на какое IRQ картируется каждая из линий запросов прерывания PCI (INTA#, INTB#, INTC#, INTD#). Для дополнительных BIOS в соответствии с установками Setup, опционально включается режим Shadow. Для System BIOS он включен всегда.

На этом этапе также программируется:

формирование NMI (Nonmaskable Interrupt) для Parity Check

формирование SMI (System Management Interrupt) для Green функций

53

Initialize time value in 40h: BIOS area.

1. If it is NOT a PNP BIOS, initialize serial and parallel ports .

2. Initialize time value in BIOS data area by translate the RTC time value into a timer tick value

.

Установка счетчика DOS Time в соответствии с Real Time Clock. Значение времени в формате часы:минуты:секунды пересчитывается в тики таймера 18.2 Hz и записывается в ячейки DOS Time в области переменных BIOS. Установка переменных BIOS, хранящих базовые адреса портов.

60

SetupVirus Protection (Boot Sector Protection) functionality according to Setupsetting

.

Установка антивирусной защиты BOOT Sector. В большинстве плат такая защита реализуется программно. Перед входом в процедуру обработки дискового сервиса (INT 13h) устанавливается транзитный программный модуль, который анализирует входные параметры функции и детектирует две ситуации:

Попытка записи в BOOT Sector (AH=3

, CL=1

, CH=0

, DL=8xh

, DH=0

)

Попытка форматирования Track 0 (AH=5

, CH=0

, DL=8xh

, DH=0

)

Если система условий - значения регистров - выполняется, вместо дисковой операции выдается предупреждающее сообщение и звуковой сигнал. На шаге 60

выполняется перестановка вектора INT 13h на транзитный контролирующий модуль, если в Setup включен данный режим.

61

1. Try to turn on Level 2 cache.

Note: if L2 cache is already turned on in POST 3D, this part will be skipped .

2. Set the boot up speed according to Setup setting .

3. Last chance for Chipset initialization .

4. Last chance for Power Management initialization (Green BIOS only) .

5. Show the system configuration table

.

Один из альтернативных моментов для включения External Cache.

Завершающие действия по инициализации Chipset и Power Management

62

1. Setup daylight saving according to Setup value .

2. Program the NUM Lock, typmatic rate and typmatic speed according to Setup setting Чтение KBD ID.

Установка режима Daylight Saving - разрешение автоматического перехода на зимнее/летнее время для RealTimeClock, состояния NUM Lock, частота автоповтора и время ожидания до входа в режим автоповтора.

63

1. If there is any changes in the hardware configuration, update the ESCD information (PNP BIOS ONLY) .

2. If there is any changes in the hardware configuration, update the DMI data pool (DMI BIOS ONLY) .

3. Clear memory that have been used .

4. Boot system via INT 19h

.

Коррекция блоков ESCD, DMI, если изменилась конфигурация. Очистка, обнуление ОЗУ.

75

Thermal Warning

.

Если в качестве контроллера системного мониторинга используется LM78, выполняется сигнализация о превышении допустимых значений температурного режима.

В настоящее время нет достоверной информации о генерации этого кода контроллерами других производителей, например Winbond Electronics или Genesys Logic.

80

...83

, 90

...93

Primary Master IDE Power Off(80)/On(90); Primary Slave IDE Power Off(81)/On(91); Secondary Master IDE Power Off(82)/On(92);

Secondary Slave IDE Power Off(83)/On(93)

.

84

and 94

Sound Chip Power Off(84)/On(94)

.

86

...88

, 96

...98

COMA Power Off(86)/On(96) ; COMB Power Off(87)/On(97) ;

LPT Power Off(88)/On(98).

8B

and 9B

Turn CRT Off(8B)/On(9B)

.

85

, 89

, 8A

, 8C

, 8D

and 95

, 99

, 9A

, 9C

, 9D

Turn Unknown Devices Off/On

.

Это не один из этапов POST, а вывод в диагностический порт контрольных точек включения / выключения неизвестных устройств.

Следует отметить, что все коды группы 80 и 90 связаны с событиями, возникающими в процессе Green Functions. На сегодня нет достоверной информации, однозначно определяющей устройства, кроме выше упомянутых, участвующих в функциях энергосбережения

B0

Spurious. If interrupt occurs in protected mode.

Обработчик-заглушка прерываний (исключений) для защищенного режима. Это не один из этапов POST, а процедура, на которую устанавливаются вектора (для защищенного режима не вектора, а дескрипторы IDT) внутренних прерываний (исключений) процессора на время работы в Protected Mode, например, при тесте Extended Memory. Если при работе в Protected Mode не будет сбоев, эта процедура и не получит управления. Если будут иметь место ошибки, например некорректные данные в дескрипторных таблицах, страничные нарушения и другие исключительные ситуации Protected Mode, управление будет передано на эту процедуру, она выведет код B0 в Port 80 и остановится

B1

If unmasked NMI occurs, display Press F1

to disable NMI, F2 reboot

.

Unclaimed NMI occurs.

Обработчик-заглушка немаскируемого прерывания. Это не один из этапов POST, а процедура, на которую указывает вектор немаскируемого прерывания. Если возник запрос NMI, и не удалось идентифицировать причину NMI, в Port80 выводится этот код, на экран выводится сообщение:

Press F1

to disable NMI, F2 to reboot

.

И ожидаются действия пользователя.

B2

Unknown action

.

55

and BB

Begin to Shutdown the system 5 Volt;

Begin to Shutdown the system 0 Volt

.

D3

SMI Handle .

D7

Software Doze

.

D8

Software Standby

.

D9

Software Suspend

.

E1

...EF

Setup Pages E1

- Page 1

, E2

- Page 2

, etc.

По этой операции проверенной информации нет, предположительно, что это актуально для старых систем, у которых доступ к BIOS ROM организуется постранично через картируемое окно, при установке каждой новой страницы выводится код Ex, где x - номер страницы. Этот факт подтверждается существованием в указанном диапазоне кодов, связанных с выполнением других процессов

EC

ECC Post Code associate with System Management Interrupt (SMI)

.

В настоящее время нет достоверной информации о причинах генерации этого кода. Предположительно, его возникновение связано с обработкой ECC в процессе выполнения Green Functions .

ED

HDD hang up on 0V resume.

Данный код сигнализирует об ошибке выхода HDD из режима энергосбережения.

FF

System Booting

.

This means that the BIOS already pass the control right to the operating system.

Передача управления загрузчику BOOT сектора. BIOS выполняет команду INT 19h. Процедура обработки прерывания INT 19h последовательно пытается заг.

POST-карта или POST-тестер это PCI плата расширения, имеющая цифровой индикатор, который выводит коды инициализации мат.платы. По данному коду можно найти, в каком из компонентов платы имеется неисправность. Коды часто зависят от производителя BIOS. Если ошибки отсутствуют и тест проходит успешно, то POST выдаёт код не меняющийся значение, к примеру на большинстве мат.плат по

завершении инициализации выводится код «FF». Также часто на тестерах установлены светодиоды отображающие напряжения +5 +3,3 +12, −12.

Вашему вниманию коды ошибок, подходящие на самые версии BIOS:

| POST-код | Описание |

|---|---|

| D0 | Предварительная инициализация чипсета материнской платы и процессора. Проверка контрольной суммы BIOS. Запрет немаскируемого прерывания NMI. Выполняется проверка контроллера Super I/O, проверка CMOS. |

| D1 | Контроллером клавиатуры выполняется процесс само-тестирования (BAT-тест). Выполняется начальная инициализация портов ввода-вывода. Инициализация контроллера DMA. |

| D2 | Запрещение использования кэш-памяти. Выполняется процедура определения объема установленной оперативной памяти. |

| D3 | Проверяется формирование запросов на регенерацию динамической оперативной памяти. Разрешение использования кэш-памяти. |

| D4 | Тестирование 512 Кбайт памяти. Выполняется установка адреса стека, настраивается кэш-память. |

| D5 | Код системной БИОС распаковывается и перезаписывается в Shadow RAM (затененную память). |

| D6 | Производится вычисление контрольной суммы БИОС и проверка нажатия комбинации клавиш Ctrl+Home. Если хотя бы одно из этих условий выполняется, запускается процедура восстановления BIOS. |

| D7 | В случае успешной проверки контрольных сумм BIOS управление передается модулю InterfaceModule, который выполняет распаковку исполняемого кода в Run-Time области. |

| D8 | Выполняется распаковка Run-Time-кода из флеш-памяти в ОЗУ. Информация CPUID сохраняется в ОЗУ. |

| D9 | Распакованный Run-Time-код переносится из области временного хранения в оперативную память. Управление передается распакованному модулю. |

| DA | Выполняется восстановление регистров CPUID. Выполняется процедура POST. |

| E0 | Инициализация регистров контроллера флоппи-дисковода. Выполняется инициализация контроллера прерываний и установка векторов прерываний. Включение кэш-памяти первого уровня. |

| E9 | Настройка регистров флоппи-дисковода. |

| EA | Выполняется проверка операции чтения с ATAPI CD-ROM и дисковой памяти. |

| EB | Возврат на контрольную точку E9 в случае возникновения ошибок при операциях с ATAPI CD-ROM. |

| EF | Возврат на контрольную точку EB в случае возникновения ошибок при операциях с дисками. |

| F0 | Выполняется поиск файла восстановления с именем AMIBOOT.ROM. |

| F1 | В точку F1 выполняется переход в том случае, если файл восстановления не найден. |

| F5 | Отключение кэш-памяти первого уровня. |

| FB | Определение типа FlashROM. Поиск во FlashROM раздела для хранения настроек чипсета. |

| F4 | В точку F4 выполняется переход в том случае, если файла восстановления с именем AMIBOOT.ROM имеет некорректный размер. |

| FC | Обнуление основного блока Flash BIOS. |

| FD | Выполняется программирование основного блока Flash BIOS. |

| FF | В точку FF выполняется переход в том случае, если программирование Flash BIOS успешно завершено. Запрещается запись у FlashROM. Выполняется отключение оборудования ATAPI. Восстанавливается значение CPUID. |

| 03 | Запрещается обработка немаскируемого прерывания (NMI), проверка ошибок четности оперативной памяти. Выполняется инициализация области данных текущего выполнения BIOS и процедуры POST. |

| 04 | Проверка контрольной суммы CMOS и напряжения питания аккумулятора. |

| 05 | Выполняется инициализация контроллера прерываний и формирование таблицы векторов прерываний. |

| 06 | Подготовка к работе интервального таймера. |

| 08 | Контроллером клавиатуры выполняется процесс само-тестирования (BAT-тест). Инициализация ЦП. |

| C0 | Запрещение использования кэш-памяти. Инициализация контроллера APIC. Подготовка процессора к работе. |

| С1 | Настройка параметров работы процессора. |

| C2 | Идентификация процессора с помощью команды CPUID. |

| C5 | Определение количества процессоров и настройка их параметров. |

| C6 | Инициализация кэш-памяти процессора. |

| С7 | Завершение процесса начальной инициализации центрального процессора. |

| 0A | Инициализация контроллера клавиатуры. |

| 0B | Выполняется поиск мыши, подключенной с помощью интерфейса PS/2. |

| 0C | Выполняется поиск клавиатуры. |

| 0E | Поиск и инициализация устройств ввода-вывода. Захват прерывания INT 09h. Вывод на экран логотипа БИОС. |

| 13 | Выполняется начальная инициализация регистров чипсета. |

| 24 | Выполняется распаковка и инициализация модулей BIOS. Подготовка к инициализации таблицы векторов прерываний. |

| 25 | Завершение инициализации таблицы векторов прерываний. |

| 2A | Выполняется инициализация устройств на локальных шинах (с помощью механизма DIM-Device Initialization Manager). Подготовка к инициализации видеоадаптера. |

| 2С | Поиск и инициализация видеокарты. |

| 2E | Выполняется поиск и инициализация дополнительных устройств ввода-вывода. |

| 30 | Выполняется инициализация компонента SMI (System Management Interrupt). |

| 31 | Распаковка модуля ADM. Инициализация и активизация ADM. |

| 33 | Инициализация модуля загрузчика. |

| 37 | Вывод на экран монитора логотип AMI, информация о версии БИОС, информации о типе процессора и его скорости. Отображение на мониторе названия клавиши, которую можно использовать для входа в Bios Setup. |

| 38 | Выполняется инициализация устройств на локальных шинах (с помощью механизма DIM-Device Initialization Manager). |

| 39 | Выполняется инициализация контроллера DMA. |

| 3A | Установка системного времени в соответствии с показаниями часов реального времени (RTC). |

| 3B | Выполняется тестирование оперативной памяти с последующим отображением на мониторе результатов теста. |

| 3C | Настройка регистров чипсета. |

| 40 | Выполняется инициализация математического сопроцессора, параллельных и последовательных портов. |

| 50 | Выполняется корректировка модулей управления памяти. |

| 52 | Выполняется корректировка информации в CMOS об объеме оперативной памяти (согласно результатам теста оперативной памяти). |

| 60 | Программирование контроллера клавиатуры на частоту авто-повтора и время ожидания до входа в режим авто-повтора согласно настройкам BIOS Setup. Установка состояния индикатора Numlock согласно настройкам BIOS Setup. |

| 75 | Выполняется инициализация прерывания INT 13h, которое используется для работы с дисковыми устройствами. |

| 78 | Создается список устройств, с которых можно выполнить загрузку ОС. |

| 7A | Выполняется инициализация остальных расширений БИОС. |

| 7C | Создание и сохранение таблицы ESCD. |

| 84 | Выполняется составление отчета об ошибках, которые были обнаружены во время прохождения процедуры POST. |

| 85 | Вывод на монитор информации об ошибках, обнаруженных во время прохождения процедуры POST. |

| 87 | На данном этапе имеется возможность войти в программу BIOS Setup. |

| 8C | Настройка регистров чипсета. |

| 8D | Выполняется построение таблицы ACPI. |

| 8E | Обслуживание NMI-прерываний. Настройка параметров периферийных устройств. |

| 90 | Выполняется завершающая инициализация SMI |

| A0 | Запрос пароля на загрузку (если в настройках BIOS Setup это предусмотрено). |

| A1 | Выполняется очистка данных, которые не требуются для загрузки ОС. |

| A2 | Подготовка модулей EFI. |

| A4 | Выполняется инициализация языкового модуля. |

| A7 | Вывод на монитор таблицы итоговых результатов прохождения процедуры POST. |

| A8 | Программирование регистров MTRR (Memory Type Range Register). |

| A9 | Ожидание ввода команд с клавиатуры. |

| AA | Сброс прерываний INT 1C, INT 09. Отключение модуля обслуживания процедур (ADM). |

| AB | Определение устройств, с которых можно выполнить загрузку ОС. |

| AC | Завершающий этап инициализации регистров чипсета в соответствии с параметрами BIOS Setup |

| B1 | Выполняется настройка интерфейса ACPI. |

| 00 | Выполнение прерывания BIOS INT 19h. Управление процессом загрузки передается загрузчику операционной системы. Начинается загрузка ОС. |

Звуковые сигналы

Встроенный динамик выдает звуковые коды ошибок во время процедуры POST.Не все системные платы для настольных ПК содержат встроенный динамик, поэтому необходимо подключить так называемую пищалку.

Сообщения об ошибках, выдаваемые BIOS

| Сообщение об ошибке | Описание |

| Обнаружен процессор, который не предназначен для использования с данной системной платой. Использование неподдерживаемых процессоров может привести к неправильной работе, повреждению системной платы для настольных ПК или процессора, или сокращению срока эксплуатации. Система отключится через 10 секунд. | Установленный процессор не совмести с системной платой для настольных ПК. |

| CMOS Battery Low | Возможна, разрядка батареи. Замените батарею. |

| CMOS Checksum Bad | Ошибка проверки контрольной суммы ОЗУ. Возможно, память CMOS повреждена. Запустите программу BIOS Setup для обновления значений. |

| Memory Size Decreased | Объем памяти уменьшился со времени последней загрузки. Если модули памяти не были удалены, возможно, память неисправна. |

| No «Boot» Device Available | Система не нашла загрузочного устройства. |

POST-коды порта 80h

Во время теста POST BIOS генерирует коды прохождения (POST-коды ) и направляет их в порт ввода/вывода 80h. Если процедура POST завершилась неудачно, последний сгенерированный POST-код остается в порту 80h. Этот код можно использовать для определения причины ошибки.

Отображение POST-кодов

Для отображения POST-кодов можно использовать один из следующих методов.

Диапазоны POST-кодов порта 80h

В таблицах ниже все POST-коды и значения представлены в шестнадцатеричном формате.

| Диапазон | Категория/Подсистема |

| 00 – 0F | Коды отладки: Могут использоваться, как средство для отладки любым модулем PEIM/драйвером |

| 10 – 1F | Процессоры системы |

| 20 – 2F | Память/набор микросхем |

| 30 – 3F | Восстановление |

| 40 – 4F | |

| 50 – 5F | Шины ввода/вывода: PCI, USB, ISA, ATA и т.д. |

| 60 – 6F | Сейчас не используется |

| 70 – 7F | Устройства вывода: Все консоли вывода |

| 80 – 8F | Зарезервировано для будущего использования (для новых кодов консоли вывода) |

| 90 – 9F | Устройства ввода: Клавиатура/Мышь |

| A0 – AF | Зарезервировано для будущего использования (для новых кодов консоли ввода) |

| B0 – BF | Загрузочные устройства: Включают в себя стационарные и съемные носители. |

| C0 – CF | Зарезервировано для использования |

| D0 – DF | |

| E0 – FF | E0 – EE: Другие коды F0 – FF: FF — ошибка прерывания процессора |

POST-коды порта 80h

| Код POST | Описание эксплуатации POST |

| 00 — 0F | Коды отладки: может использоваться, как средство для отладки любым модулем PEIM/диском |

| 10 — 1F | Процессор системы |

| 10 | Включение процессора системы (загрузочный процессор) |

| 11 | Инициализация кэш-памяти процессора (включая SP) |

| 12 | Начало инициализации приложений процессора |

| 13 | Инициализация SMM |

| 14 | Инициализация сетевого подключения |

| 15 | Преждевременный выход при инициализации драйвера платформы |

| 16 | Инициализация драйвера SMBUS |

| 17 | Вход в исполнимый код SMBUS в режиме чтения/записи |

| 19 | Вход в режим программирования тактового генератора CK505 |

| 1F | Невосстановимая ошибка процессора |

| 20 — 2F | Память/набор микросхем |

| 21 | Инициализация компонентов набора микросхем |

| 22 | Чтение SPD через модули памяти DIMM |

| 23 | Идентификация модулей памяти DIMM |

| 24 | Программирование параметров тактовой частоты с помощью контроллера памяти и модулей DIMM |

| 25 | Конфигурирование памяти |

| 26 | Оптимизация установок памяти |

| 27 | Инициализация памяти, например ECC |

| 28 | Тестирование памяти |

| 2F | Системе не удалось обнаружить память или пригодную память |

| 30 — 3F | Восстановление |

| 30 | Восстановление после сбоя было запущено по запросу пользователя |

| 31 | Восстановление после сбоя было запущено ПО (повреждено флэш-устройство) |

| 35 | Передача управления капсуле восстановления |

| 3F | Невозможно восстановить |

| 50 — 5F | Шины ввода/вывода (PCI, USB, ISA, ATA и т.д) |

| 50 | Нумерация шин PCI |

| 51 | Передача ресурсов на шину PCI |

| 52 | Инициализация контроллера Hot Plug PCI |

| 53 – 57 | Зарезервировано для шины PCI |

| 58 | Переустановка шины USB |

| 59 | Зарезервировано для USB |

| 5A | Переустановка шины PATA/SATA и всех устройств |

| 5B | Зарезервировано для ATA |

| 5C | Переустановка SMBUS |

| 5D | Зарезервировано для SMBUS |

| 5F | Невосстановимая ошибка шины ввода/вывода |

| 60 — 6F | Сейчас нет действительных POST-кодов в диапазоне 60 — 6F.

Если POST-код будет отображен в данном диапазоне, это код из диапазона B0 — BF. (На 7-сегментном ЖК-дисплее, символ ‘b’ выглядит как 6). Пример: |

| 70 — 7F | Устройства вывода |

| 70 | Переустановка контроллера VGA |

| 71 | Отключение контроллера VGA |

| 72 | Включение контроллера VGA |

| 78 | Переустановка контроллера консоли |

| 79 | Отключение контроллера консоли |

| 7A | Включение контроллера консоли |

| 7F | Невосстановимая ошибка устройства вывода |

| 90 — 9F | Устройства ввода |

| 90 | Переустановка клавиатуры |

| 91 | Отключение клавиатуры |

| 92 | Определение присутствия клавиатуры |

| 93 | Включение клавиатуры |

| 94 | Очистка входного буфера клавиатуры |

| 95 | Информация о контроллере клавиатуры — запуск самотестирования (только PS2) |

| 98 | Переустановка мыши |

| 99 | Disabling mouse |

| 9A | Определение присутствия мыши |

| 9B | Включение мыши |

| 9F | Невосстановимая ошибка устройства ввода (клавиатура или мышь) |

| B0 – BF | Загрузочные устройства |

| B0 | Переустановка стационарных носителей |

| B1 | Отключение стационарных носителей |

| B2 | Определение присутствия стационарных носителей (обнаружение жесткого диска IDE и т.д.) |

| B3 | Подключение/настройка стационарных носителей |

| B8 | Переустановка съемных носителей |

| B9 | Отключение съемных носителей |

| BA | Определение присутствия съемных носителей (обнаружение IDE, CD-ROM и т.д.) |

| BC | Подключение/настройка съемных носителей |

| BF | Невосстановимая ошибка загрузочного устройства |

| D0 – DF | Выбор загрузочного устройства |

| Dy | Перезагрузка через параметр y (y=от 0 до 15) |

| E0 – FF | Другие коды |

| E0 | Начато распределение PEIM (возникает при первом сообщении EFI_SW_PC_INIT_BEGIN EFI_SW_PEI_PC_HANDOFF_TO_NEXT) |

| E2 | Обнаружена постоянная память |

| E1, E3 | Зарезервировано для PEI/PEIM |

| E4 | Начало фазы DXE |

| E5 | Начало распределения драйверов |

| E6 | Начало соединения драйверов |

| E7 | Ожидание воода данных пользователем |

| E8 | Проверка пароля |

| E9 | Вход в утилиту BIOS Setup |

| EB | Вызов установленных дополнительных ПЗУ |

| F4 | Вход в режим сна |

| F5 | Выход из режима сна |

| F8 | Произошел вызов службы загрузки EFI ExitBootServices () |

| Была вызвана служба выполнения работы EFI SetVirtualAddressMap ()

|

|

| FA | Произошел вызов службы прогона EFI ResetSystem () |

| FF | Ошибка процессора |

Типичный порт 80-я последовательность POST

Обычно значения кодов порта 80h увеличиваются в процессе загрузки. Меньшие значения кодов относятся к подсистемам, расположенным ближе к процессору, а большие значения кодов – к периферийным устройствам. Обычно используется следующий порядок инициализации: Процессор -> Память -> Шины -> Устройства ввода-вывода -> Устройства загрузки. Последовательность POST-кодов зависит от используемой системы.

13Инициализация SMM50Нумерация шин PCI51Передача ресурсов на шину PCI92Обнаружение присутствия клавиатуры90Переустановка клавиатуры94Очистка входного буфера клавиатуры95Самотестирование клавиатурыEBВызов графических режимов BIOS58Переустановка шины USB5AПереустановка шины PATA/SATA и всех устройств92Обнаружение присутствия клавиатуры90Переустановка клавиатуры94Очистка входного буфера клавиатуры5AПереустановка шины PATA/SATA и всех устройств28Тестирование памяти90Переустановка клавиатуры94Очистка входного буфера клавиатурыE7Ожидание воода данных пользователем01INT 1900Готово для перезагрузки

American Megatrends, Inc. (AMI)

Контрольные точки процедур POST, выполняемых в AMIBIOS, были переработаны и дополнены в 1995 году и до настоящего времени не претерпели существенных изменений. Первое описание POST кодов или как их называет AMI - "check points" в их нынешнем виде появилось в связи с выходом в свет ядра V6.24, 15/07/95. Некоторые изменения внесены в AMIBIOS V7.0, что отражается в настоящем документе.

Особенности выполнения стартовых процедур AMIBIOS

Если в процессе старта в диагностическом порту появляются данные 55h, AAh, не следует сопоставлять эту информацию с POST кодами - мы имеем дело с типовой тестовой последовательностью, в задачи которой входит проверка целостности шины данных.

На этапе старта вывод в диагностический порт данных носит специфический для каждой платформы характер. В некоторых реализациях первый визуализируемый код связан с действиями, который компания AMI называет chipset specific stuff. Эта процедура сопровождается выводом в порт 80h значения CCh и выполнением ряда действий по настройке регистров системной логики. Как правило, код CCh возникает в тех случаях, когда используется системная логика от Intel, построенная на основе контроллера

PIIX - это чипсеты TX, LX, BX.

Некоторые бортовые микросхемы ввода-вывода содержат RTC и контроллер клавиатуры, которые по старту находятся в отключенном состоянии. Цель BIOS - проинициализировать эти ресурсы платы для дальнейшего использования. В этом случае первая стартовая процедура, связанная с настройкой контроллера клавиатуры, сопровождается выводом значения 10h, затем выполняется инициализация RTC, о чем свидетельствует появление в диагностическом порту кода DDh. Следует отметить, что отказ хотя бы одного из этих ресурсов повлечет нестарт системной платы в целом на первом же этапе выполнения POST.

На ряде плат процесс инициализации начинается с перевода CPU в защищенный режим. В этом случае вслед за первым визуализируемым кодом 43h выполнение POST продолжается так, как описано в документации AMIBIOS - управление передается в точку D0h.

Коды неупакованной процедуры инициализации

(Uncompressed Init Code Check Points)

EE В современных реализациях AMIBIOS первый визуализируемый код связан с об ращением к устройству, с которого возможна загрузка для восстановления BIOS

CC Инициализация регистров системной логики

CD Тип Flash ROM не опознан

CE Несовпадение контрольных сумм в стартовом BIOS

CF Ошибка в доступе к запасной микросхеме Flash ROM

DD Ранняя инициализация RTC, который интегрирован в SIO чип

D0 Запрет немаскируемого прерывания NMI. Отработка временной задержки для затухания переходных процессов. Проверка контрольной суммы Boot Block, останов при несовпадении

D1 Выполнение процедуры регенерации памяти и Basic Assurance Test. Переход в 4 GB режим адресации памяти

D3 Определение объема и первичный тест памяти

D4 Возврат в реальный режим адресации памяти. Ранняя инициализация чип сета Установка стека

D5 Перенос модуля POST из Flash ROM в транзитную область памяти

D6 При несовпадении контрольной суммы или CTRL+Home выполняется переход на процедуру восстановления Flash ROM (Код E0)

D7 Передача управления служебной программе, осуществляющей распаковку системного BIOS

D8 Полная распаковка системного BIOS

D9 Передача управления системному BIOS в Shadow RAM

DA Чтение информации из SPD (Serial Presence Detect) модулей DIMM

DB Настройка MTRR регистров центрального процессора

DC Контроллер памяти программируются согласно данным, полученным из SPD

DE Ошибка конфигурации системной памяти. Фатальная ошибка

DF Ошибка конфигурации системной памяти. Звуковой сигнал

10 Ранняя инициализация контроллера клавиатуры

11 Возврат из состояния STR (Suspend to RAM)

12 Восстановление доступа к SMRAM (System Management RAM)

13 Восстановление регенерации памяти

14 Поиск и инициализация VGA BIOS Коды процедуры перезаписи Flash ROM (Boot Block Recovery Codes)

E0 Выполняется подготовка к перехвату INT19 и проверяется возможность старта системы в упрощенном режиме

E1 Установка векторов прерываний

E3 Восстановление содержимого CMOS, поиск и инициализация BIOS

E2 Подготовка контроллеров прерываний и непосредственного доступа к памяти

E6 Разрешение прерываний от системного таймера и FDC

EC Повторная инициализация контроллеров IRQ и DMA

ED Инициализация дисковода

EE Чтение загрузочного сектора с дискеты

EF Ошибка дисковых операций

F0 Поиск файла AMIBOOT.ROM

F1 В корневом каталоге файл AMIBOOT.ROM не найден

F2 Считывание FAT

F3 Считывание AMIBOOT.ROM

F4 Объем файла AMIBOOT.ROM не соответствует объему Flash ROM

F5 Запрет Internal Cache

FB Определение типа Flash ROM

FC Стирание основного блока Flash ROM

FD Программирование основного блока Flash ROM

FF Рестарт BIOS Коды распакованного системного BIOS, выполняемые в ShadowRAM

(Runtime code is uncompressed in F000 shadow RAM)

03 Запрет немаскируемого прерывания NMI. Определение типа сброса

05 Инициализация стека. Запрет кэширования памяти и контроллера USB

06 Выполнение в ОЗУ служебной программы

07 Распознавание процессора и инициализация APIC

08 Проверка контрольной суммы CMOS

09 Проверка отработки клавиш End/Ins

0A Проверка сбоя батарейного питания

0B Очистка буферных регистров контроллера клавиатуры

0C Контроллеру клавиатуры передается команда тестирования

0E Поиск дополнительных устройств, обслуживаемых контроллером клавиатуры

0F Инициализация клавиатуры

10 Клавиатуре передается команда сброса

11 Если нажата клавиша End или Ins, выполняется сброс CMOS

12 Перевод в пассивное состояние контроллеров DMA

13 Инициализация чип сета и кэш L2

14 Проверка системного таймера

19 Выполняется тест формирования запросов на регенерацию DRAM

1A Проверка длительности цикла регенерации

20 Инициализация устройств вывода

23 Считывается порт ввода контроллера клавиатуры. Опрашивается Keylock Switch и Manufacture Test Switch

24 Подготовка к инициализации таблицы векторов прерываний

25 Инициализация векторов прерываний завершена

26 Через порт ввода контроллера клавиатуры опрашивается состояние перемычки Turbo Switch

27 Первичная инициализация контроллера USB. Обновление микрокода стартового процессора

28 Подготовка к установке видеорежима

29 Инициализация LCD панели

2A Поиск устройств, обслуживаемых дополнительными ROM

2B Инициализации VGA BIOS, проверка его контрольной суммы

2C Выполнение VGA BIOS

2D Согласование INT 10h и INT 42h

2E Поиск видеоадаптеров CGA

2F Тест видеопамяти адаптера CGA

30 Тест схем формирования разверток адаптера CGA

31 Ошибка видеопамяти или схем формирования разверток. Поиск альтернативного видеоадаптера CGA

32 Тест видеопамяти альтернативного видеоадаптера CGA и схем разверток

33 Опрос состояния перемычки Mono/Color

34 Установка текстового режима 80х25

37 Видеорежим установлен. Экран очищен

38 Инициализация бортовых устройств

39 Вывод сообщений об ошибках на предыдущем шаге

3A Вывод сообщения «Hit DEL» для входа в CMOS Setup

3B Начало подготовки к тесту памяти в защищенном режиме

40 Подготовка дескрипторных таблиц GDT и IDT

42 Переход в защищенный режим

43 Процессор в защищенном режиме. Прерывания разрешены

44 Подготовка к проверке линии A20

45 Тест линии A20

46 Определение размера ОЗУ выполнено

47 Тестовые данные записаны в Conventional Memory

48 Повторная проверка Conventional Memory

49 Тест Extended Memory

4B Обнуление памяти

4C Индикация процесса обнуления

4D Запись в CMOS полученных размеров Conventional и Extended memory

4E Индикация реального объема системной памяти

4F Выполняется расширенный тест Conventional Memory

50 Коррекция размера Conventional Memory

51 Расширенный тест Extended Memory

52 Объемы Conventional Memory и Extended Memory сохранены

53 Обработка отложенных ошибок четности

54 Запрет контроля четности и обработки немаскируемых прерываний

57 Инициализация региона памяти для POST Memory Manager

58 Выводится приглашение для входа в CMOS Setup

59 Возврат процессора в реальный режим

60 Проверка страничных регистров DMA

62 Тест регистров адреса и длины пересылки контроллера DMA#1

63 Тест регистров адреса и длины пересылки контроллера DMA#2

65 Программирование контроллеров DMA

66 Очистка регистров Write Request и Mask Set POST

67 Программирование контроллеров прерываний

7F Разрешение запроса NMI от дополнительных источников

80 Устанавливается режим обслуживания прерываний от порта PS/2

81 Тест интерфейса клавиатуры при ошибках сброса

82 Установка режима работы контроллера клавиатуры

83 Проверка статуса Keylock

84 Верификация объема памяти

85 Вывод на экран сообщений об ошибках

86 Настройка системы для работы Setup

87 Распаковка программы CMOS Setup в Conventional Memory.

88 Работа программы Setup завершена пользователем

89 Завершено восстановление состояния после работы Setup

8B Резервирование памяти дополнительному блоку переменных BIOS

8C Программирование конфигурационных регистров

8D Первичная инициализация контроллеров HDD и FDD

8F Повторная инициализация контроллера FDD

91 Конфигурирование контроллера жестких дисков

95 Выполняется ROM Scan для поиска дополнительных BIOS

96 Дополнительная настройка системных ресурсов

97 Проверка сигнатуры и контрольной суммы дополнительного BIOS

98 Настройка System Management RAM

99 Установка счетчика таймера и переменных параллельных портов

9A Формирование списка последовательных портов

9B Подготовка области в памяти для теста сопроцессора

9C Инициализация сопроцессора

9D Информация о сопроцессоре сохраняется в CMOS RAM

9E Идентификация типа клавиатуры

9F Поиск дополнительных устройств ввода

A0 Формирование регистров MTRR (Memory Type Range Registers)

A2 Сообщений об ошибках на предыдущих этапах инициализации

A3 Установка временных характеристик автоповтора клавиатуры

A4 Дефрагментирование неиспользованных регионов RAM

A5 Установка видео режима

A6 Очистка экрана

A7 Перенос исполняемого кода BIOS область Shadow RAM

A8 Инициализация дополнительного BIOS в сегменте E000h

A9 Возврат управления системному BIOS

AA Инициализация USB шины

AB Подготовка модуля INT13 для обслуживания дисковых сервисов

AC Построение таблиц AIOPIC для поддержки мультипроцессорных систем

AD Подготовка модуля INT10 для обслуживания видео сервисов

AE Инициализация DMI

B0 Таблица конфигурации системы выведена

Особенности выполнения Device Initialization Manager

Кроме выше указанных POST кодов, в диагностический порт выводятся сообщения о событиях в процессе выполнения Device Initialization Manager (DIM). Существует несколько контрольных точек, в которых отображается состояние инициализации системных или локальных шин.

2A Инициализация устройств на системной шине

39 Индикация ошибок, возникающих при инициализации шин

95 Инициализация шин, управляемых с помощью дополнительных BIOS DE Ошибка конфигурации системной памяти

DF Ошибка конфигурации системной памяти

Информация отображается в формате слова, младший байт которого совпадает с системным POST кодом, а старший байт указывает на тип выполняемой инициализациионной процедуры. Старшая тетрада в старшем байте указывает тип выполняемой процедуры, а младшая определяет шинную топологию для ее применения.

Старшая тетрада:

0 инициализация всех устройств на всех шинах запрещена

1 инициализация статических устройств

2 инициализация устройств вывода информации

3 инициализация устройств ввода информации

4 инициализация устройств системной загрузки (IPL)

5 инициализация устройств общего назначения

6 сообщение об ошибках

7 инициализация устройств, управляемых дополнительными ROM

Младшая тетрада:

0 системные процедуры инициализации (DIM)

1 шины подключения бортовых устройств

2 шина ISA Legacy

3 шина EISA

4 шина ISA PnP

5 шина PCI

6 шина PCMCIA

7 шина MCA

В случае если обнаружена ошибка конфигурации системной памяти, в порт 80h выводится последовательно в бесконечном цикле код DE, код DF, код ошибки конфигурации, который может принимать следующие значения:

00 Оперативная память не обнаружена

01 Установлены модули DIMM различных типов (пример, EDO и SDRAM)

02 Чтение содержимого SPD закончилась неудачей

03 Модуль не соответствует требованиям для работы на заданной частоте

04 Модуль не может быть использован в данной системе

05 Информация в SPD не позволяет использовать установленные модули

06 Обнаружена ошибка в младшей странице памяти

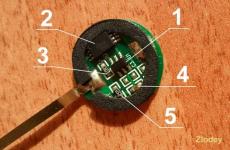

PI0049

POST-карта для дефектации компьютерных материнских плат, модель PI0049, предназначена для ото-бра-же-ния POST-кодов всех производителей BIOS. Данное изделие более известно под названием PC Ana-lyz-er 2 , особенности функционирования которого неоднократно рассматривались на страницах нашего сайта. Руководство пользователя содержит перечень инженерных паролей, а также список стандартных сочетаний клавиш для входа в BIOS . Разработка POST-карты защищена патентом 01224987.4 (Китай).

PI0050

POST-карта IC80 V5.0

QiGuan KLPI6

Диагностическая карта KLPI6-SD производства QiGuan Electronics выполнена в соответствии с нормами международного стандарта IEC 61010-1, устанавливающему требования к низковольтному испы-та-тель-но-му оборудованию по перенапряжению. Функциональная особенность POST-карты KLPI6-SD — воз-мож-ность индикации POST-кодов персонального компьютера на внешней дисплейной панели. Кроме те-ку-ще-го кода на обеих индикаторах отображаются предыдущие значения, а также POST-код фатального сбоя.

QiGuan MKCP6A

Плата для диагностики персональной платформы и тестирования ее на стабильность (Diagnostics and Stability Test Card), модель MKCP6A , разработана компанией QiGuan Electronics с использованием технологии, защищенной национальным патентом 03126857.9 (Китай). Для отображения ПОСТ-кодов на плате имеется три пары(!) индикаторов: первая пара предназначена для вывода сбойного кода, следующая выводит текущий POST-код, последняя — предыдущий код.

SL-M04A

Раритетная версия руководства пользователя на турецком языке к диагностическому POST-контроллеру PC Analyzer (по-турецки PC Analizoru). Кроме широко известных описаний POST-кодов включает в себя перечень контрольных точек почти всех известных производителей BIOS. Для удобства все пост-коды отсортированы по номеру, что облегчает доступ и понимание. Комментарии к ним следуют не-по-сред-ствен-но за кодом и разделены названием BIOS.

25.10.2019